Москва, ш. Очаковское,

д. 28 стр. 2, офис 75

Москва, ш. Очаковское,

д. 28 стр. 2, офис 75

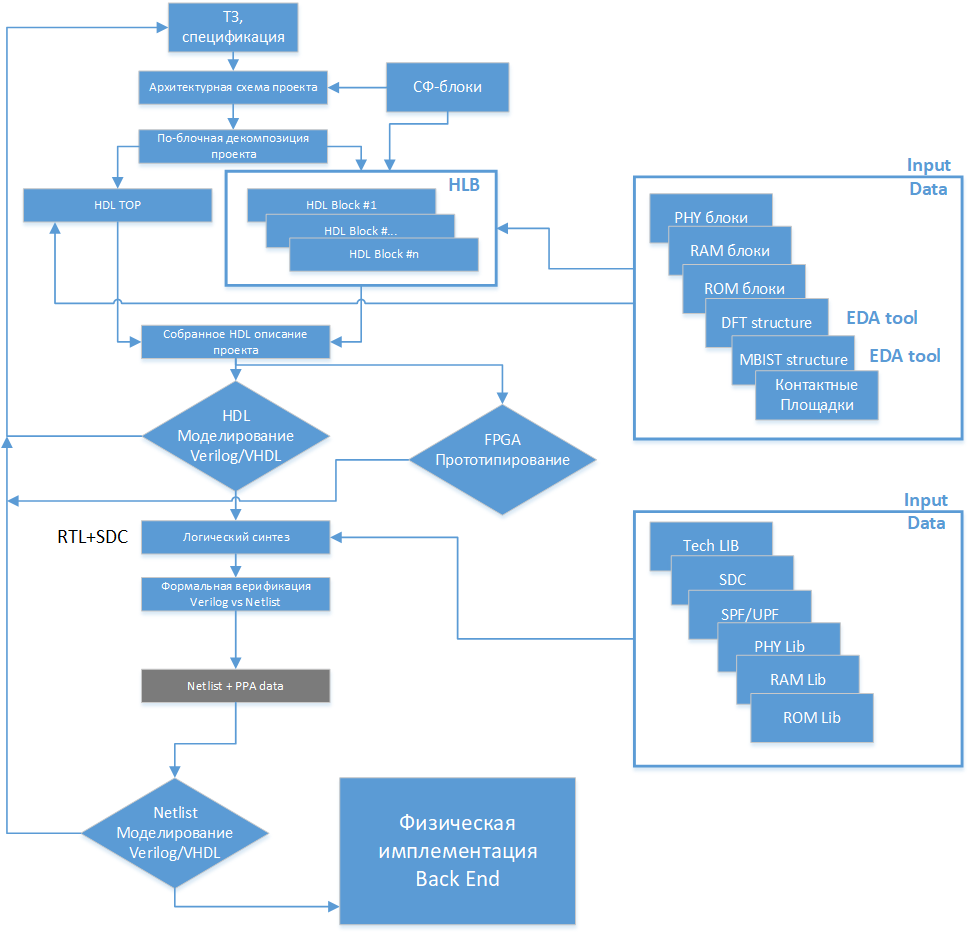

Полный цикл проектирования СБИС

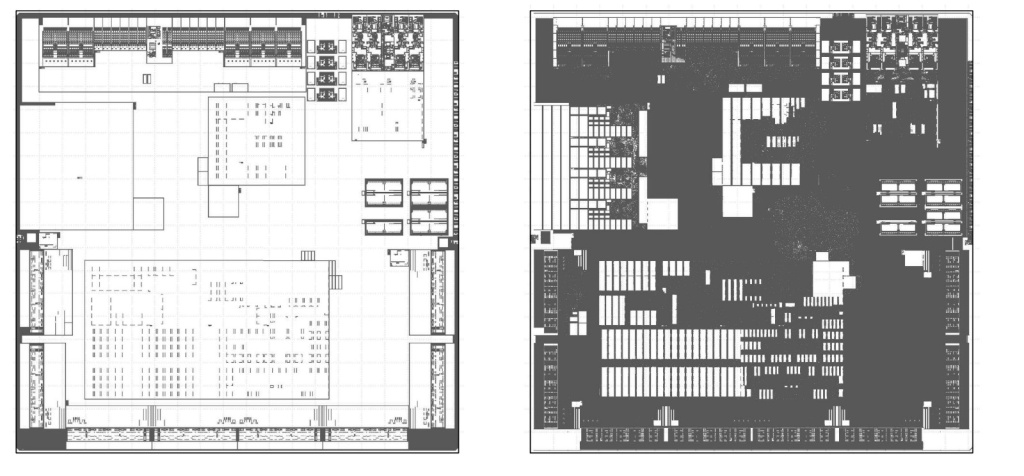

Собственный дизайн-центр проектирования цифровых СБИС, СФ-блоков от RTL до GDS;

Разработка архитектурного решения;

Разработка, функциональная верификация СФ-блоков;

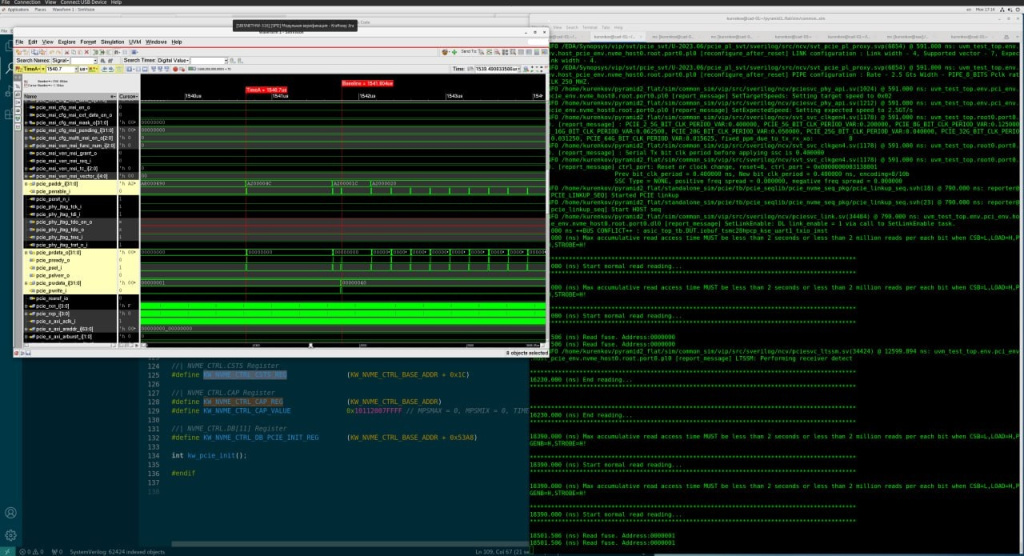

HDL интеграционная сборка проекта, функциональная верификация;

Front End проектирование – логический синтез и формальная верификация;

Back End проектирование – топологический синтез DRC, LVS, DFM

Производство

Изготовление кристаллов, сборка в корпус, логистика;

Изготовление комплекта масок, пластин, фабричное тестирование.

FPGA разработка

FPGA прототипирование цифровых СФ-блоков;

Функциональная верификация СФ-блоков на FPGA моделях;

Сборка и прототипирование проектов СнК (система на кристалле) на FPGA

Платы для создания прототипов и платформ валидации на основе:

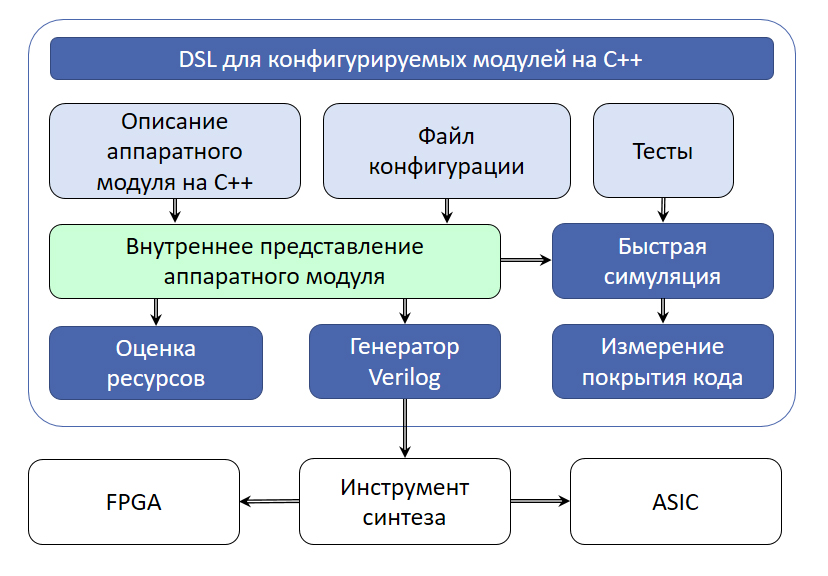

Для проектирования и симуляции сложнофункциональных блоков разработчики RTL кода используют как классические инструменты, так и специализированные программные пакеты, разработанные в России. В частности, некоторые СФ-блоки проектов создаются с помощью программного комплекса высокоуровневого языка описания аппаратуры (HDL) «Инструментарий разработки интегральных схем (система ИРИС)». Авторами ИРИС являются научные сотрудники механико-математического факультета Московского государственного университета имени М.В. Ломоносова. Система ИРИС является полностью российской разработкой, что позволяет с легкостью корректировать вектор ее развития и в дальнейшем интегрировать ее в стек российских средств разработки микроэлектроники.

Структурная схема системы ИРИС

К неоспоримым преимуществам системы ИРИС можно отнести высокую скорость разработки, использование знакомого большинству разработчиков языка программирования, полное соответствие принятым в индустрии стандартам, самодостаточность системы и ее хорошую функциональную совместимость с популярными средствами разработки других производителей.

Система ИРИС является высокоуровневым языком описания аппаратуры (HDL), нацеленным на быстрое создание и тестирование сложных аппаратных модулей;

Она реализована в виде библиотеки С++, одного из самых популярных языков программирования, для которого существует большой выбор высокоэффективных компиляторов (Visual Studio, GCC, CLang). Выбор языка популярного языка C++ особенно важен в данном ключе, поскольку это значительно понижает порог входа в проектирование для большинства инженеров, и так хорошо знакомых с ним;

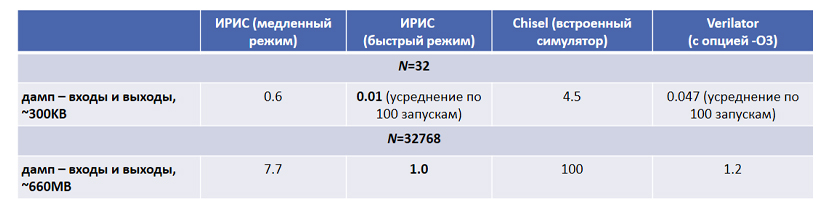

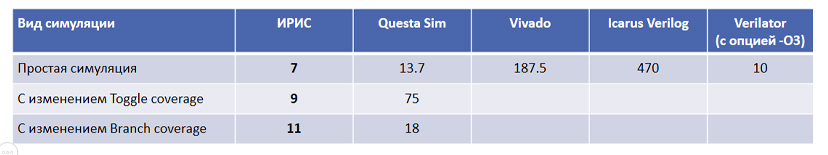

Система обладает встроенным сверхбыстрым симулятором, позволяющим избежать использования внешних средств (Verilator, Questa Sim, Vivado и др.) и работающим многократно быстрее, чем встроенный симулятор Chisel.

Скорость симуляции (Mersenne Twister, N бит за такт, сек.)

Скорость симуляции (СФ блок LDPC декодер для ТНИ, сек.)

Создание аппаратной модели (RTL Verilog) является наиболее затратным и долгим этапом (1.5-2 года) при проектировании. Многочисленные примеры использования ИРИС при проектировании сложных микросхем доказали, что время на проектирование сокращается в несколько раз.

Возможность создавать, отлаживать, симулировать СФ-блок в среде разработки ИРИС и получать на выходе отлаженный RTL Verilog-код позволяет сократить количество используемых инструментов коммерческих САПР в маршруте проектирования ИМС. Так, например, при использовании полностью отлаженного RTL кода можно не проводить Verilog моделирование RTL средствами Xcelium (Cadence), VCS (Synopsys) и сразу переходить к этапу логического синтеза. Соответствие полученного списка межсоединений библиотечных элементов, так называемого netlist, исходному RTL устанавливается с помощью проверки логической эквивалентности, что позволяет также опустить и этап Verilog моделирования в netlist.

Получаемое Verilog-описание разработанных СФ-блоков удовлетворяет стандарту 1364-2005 - IEEE Standard for Verilog Hardware Description Language (файлы с расширением .v), что позволяет использовать различные версии, в том числе и самые современные, инструментов логического синтеза Genus (Cadence), Design Compiler (Synopsys), Vivado (Xilinx). Для наблюдения за временными диаграммами ИРИС генерирует файлы в стандартизированном формате Value Change Dump (VCD), определенном в стандарте IEEE Standard 1364-2001 (расширение .vcd). При необходимости это даёт разработчику дополнительные возможности подключать и использовать визуализацию в средствах моделирования Xelium (Cadence), VCS (Synopsys).

Разработка программного кода, HDL описаний с использованием языков программирования С, С++, Verilog/System Verilog - семейств.

Разработка программного кода цифровых сложно-функциональных (СФ) блоков для применения в СнК, таких как высокоскоростные периферийные устройства, блоки реализующие сложные математические функции кодирования-декодирования и других алгоритмов и другие.

Интеграция компонент проекта на верхнем (ТОР) уровне.

Выработка конфигурации контроллеров, реализация интерфейсной связки контроллера и физической части, формирование файла временных ограничений, расчёт и подстановка блоков памяти.

Проведение HDL моделирования, и логического синтеза, формальной верификации, физического синтеза и финальных проверок конструкторско-технологических ограничений для получения финального GDSII файла.

Реализация подходов Digital on Top Flow.

Проверка разработанных Verilog RTL описаний, полученных с помощью трансляции программного кода, конструктива языка программирования С, системой ИРИС

FPGA прототипирование разрабатываемых СФ-блоков на основе аппаратуры Xilinx Ultrascale+

Разработка моделей устройства реализующей наиболее значимый набор основных функций.

С момента основания центра в 2022 году велась планомерная работа по созданию инфраструктуры дизайн-центра, которая на сегодня включает в себя СХД, высокопроизводительные серверы и FPGA стенды, рабочие места, специализированное программное обеспечение и мощное вычислительное оборудование для выполнения различных типов задач (в т.ч. высокопроизводительные САПР для разработки на базе FPGA и ASIC).

Оснащение дизайн-центра соответствует мировым стандартам и является уникальным, поскольку позволяет не только разрабатывать ИМС, СБИС и СнК, но и проводить комплексное тестирование полученных технических образцов для различных видов нагрузок.